m代码

我是先从通信原理书上了解了卷积码的概念,再结合网上部分资料,勉强搞懂,感觉主要需要掌握卷积码编码器、状态图、网状图。基本概念太多,要叙述起来需要花挺多时间的,不过网上这部分资料挺多的,这里就不在全部叙述,仅就部分知识点说一下我的看法。

1.1 编码器状态

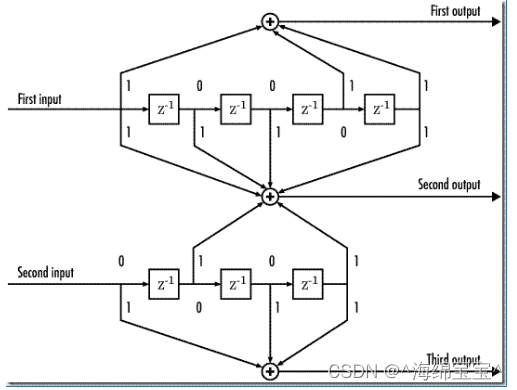

以(2,1,2)卷积码例,此时编码器对应的状态共有2^2=4种,如图2所示。

由于输入只有0或者1,故每一种状态对应的下一种状态都只有两种情况。值得一提的是,这两种情况对应的输出相互取反,如果一个输入为01,则另一种输入为10,即码距最大。后面我也去理解了一下Viterbi译码,由这个译码原理,我进一步发现 编码时一个状态对应不同的输出互相取反的情况是有必要的,是有特殊规定的。因为这样的规定可以使得最大似然译码(MLD) 算法可以在Viterbi译码中成功应用。(由于本篇只论述编码,我还没开始译码的仿真,所以此处不再继续叙述译码。后面了解译码并仿真成功后再进一步叙述我对译码的理解)。

本实验以(2,1,2)为例。必须知道如何通过生成多项式画出编码器结构,或者从编码器结构写出生成多项式,这部分内容B上面很多讲的挺详细的视频。本次实验的生成多项式为

%一般用八进制表示,为了方便,我用的是二进制。

m = [1 0 0;1 1 1]; m代码 %第n行元素分别表示每个编码器(从左至右)与第n个输出码元的连接情况,即行数代表输出码元数 列数代表编码器个数 即m+1

此代码模仿自这位大佬的作品实验七-卷积编码的MATLAB实现

(如有侵权,告知后立马删!)

经过验证,此函数的卷积编码输出与在MATLAB中直接调用poly2trellis及convenc函数卷积编码后的输出一致。

做完(n,1,m)的卷积编码还不能 罢休,我的任务是完成(n,k,m)的编码与译码,所以首先我还得把(n,k,m)码给仿真出来,这样才算真正理解了。但是网上这部分资料比较少,好在被我发现了一个宝藏文章,自取。poly2trellis(matlab)

罢休,我的任务是完成(n,k,m)的编码与译码,所以首先我还得把(n,k,m)码给仿真出来,这样才算真正理解了。但是网上这部分资料比较少,好在被我发现了一个宝藏文章,自取。poly2trellis(matlab)

在搜索怎么使用MATLAB的时候发现了这个宝藏,让我受益匪浅。从这篇文章可以看出来,实际k个输入就有点类似于k个(n,1,m)卷积码的相叠加,就是把最后结果取异或而已。于是抱着试一试的态度,我又继续尝试了,在于BUG一番斗争后,功夫不负有心人,我成功了!!!!

以(3,2,[2 2])为例,生成多项式为

G1{1} = [1 0;0 1;1 1];每个元组中对应一个信息码所在编码器的结构

G1{2} = [0 1;1 1;1 1];

中途由于马虎出了一些问题,最终终于成功实现。后面还进行了另一组实验,仍然正确。

总的来说,卷积码相对分组码来说更难理解。这次很幸运地理解了卷积码的编码过程并成功仿真出来,还是很自豪的。不过编码要比译码更简单,后面的译码才更是一块硬骨头,目前已经有一定的了解了,打算继续进一步了解,并尝试去仿真,希望下一次译码仿真不会太久!

(内容如有侵权,我知道后立马删除)

关于本文对于卷积码参数定义的理解如下:

比如图中所示,有两个输入,三个输出,第一个输入对应的有4个移位寄存器,第二个输入对应的有3个移位寄存器。那么按照本文中的叙述的,这个卷积编码器表示应该为:(3,2,[4+1=5 3+1=4]),然后生成多项式应该是有两个,第一个输入对应的生成多项式为:[1 0 0 1 1;1 1 1 0 1;0 0 0 0 0](每一行对应一个输出的表达式,每行5个元素);第二个输出对应的生成多项式为:[0 0 0 0;0 1 0 1;1 0 1 1];(因为第二个输入对应的移位寄存器只有三个,对应三个输出,再加上一个本来的输入,所以这里对应的每一行只有四个元素),其中0表示没用到,1表示用到了。

链接: https://pan.baidu.com/s/1zzeTahGPpvrQz7JZJWqLPQ?pwd=c1hv 提取码: c1hv